RISC-V Summit, which takes place virtually on December 8-10, will bring hundreds of developers together to network with thought leaders, technology companies and researchers spearheading the adoption of open standard collaboration.

Zephyr RTOS will be featured in a few of the presentations next week including a keynote panel with Zephyr Project members Antmicro and Google. Check out the sessions below and add them to your schedule.

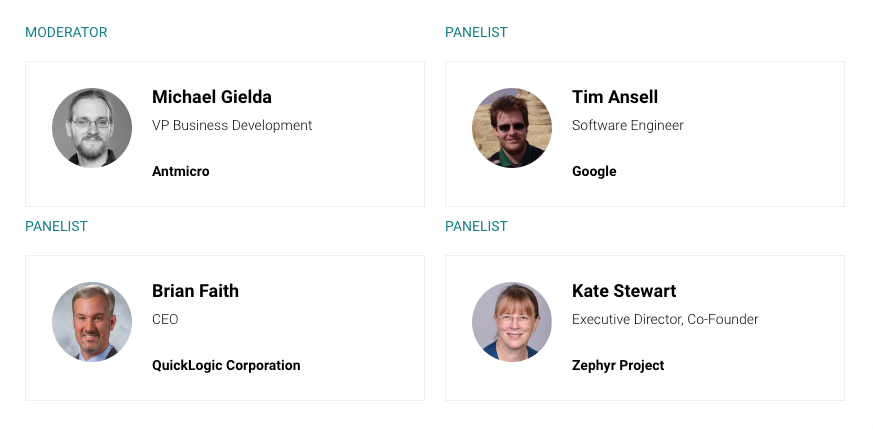

On Tuesday, December 8 at 10-10:30 am: Building an Open Edge Machine Learning Ecosystem with RISC-V, Zephyr, TensorFlow Lite Micro and Renode. Led by Michael Gielda (Antmicro), Tim Ansell (Google), Kate Stewart (Zephyr Project) and Brian Faith (QuickLogic).

By moving closer to the edge, machine learning is profoundly changing the IoT landscape, where RISC-V is already seeing immense success. To be able to fully capitalize on the opportunities that arise from this trend, as well as tackle the related challenges, various communities must come together to create an open ecosystem of modern tools, frameworks and platforms that together will constitute a seamless environment for developers to build advanced ML applications on RISC-V.

The keynote panel will feature a discussion of how the strengths of RISC-V, Zephyr RTOS, TensorFlow Lite and Renode can be combined to provide collaborative, software-driven, traceable ML development for the very edge. The participants will discuss how the vendor-neutral approach of RISC-V resonates with the foundational principles of the Zephyr RTOS and the Renode simulation framework, and how TensorFlow Lite Micro can leverage the open ISA and its tools to innovate in the ML domain also on the hardware level, e.g. using FPGAs or custom extensions. The discussion will also touch upon modern testing methodologies and HW-SW co-development enabled by Renode – already employed by Zephyr, Google’s TF Lite Team and QuickLogic – enabling efficient, deterministically testable ML development on RISC-V.

On Wednesday, December 9 at 1:30 – 1:50 pm, Gajinder Panesar, Fellow at Mentor, A Siemens Business, and Peter Claydon, President of Picocom, will present “RISC-V in 5G New Radio Small Cell Base Stations.”

Modern cellular communications use the Orthogonal frequency-division multiple access (OFDMA) air interface. In such a system, data is transmitted in symbols which are grouped in slots. In 5G these slots can range from 0.25 and 0.125 ms. The scheduling of the traffic carried in these slots is done by the MAC layer. It schedules traffic to the network (uplink) as well from the network to the User (downlink).

Efficient 5G base stations are being designed and deployed to handle not just many, many users supporting many 5G cells but even have support for several separate mobile operators. Each operator may require its own software.

The physical layer (PHY) must process the data (both control and user) passed to it by the MAC to fill in the slots and symbols for transmission and reception. If the PHY fails to meet the strict timing constraints whole slots of data will be lost requiring recovery mechanisms.

In this talk we present a heterogeneous SoC which implements a 5G NG small cell base station using clusters of RISCVs and dedicated DSPs. Each of the RISCVs will be running Zephyr OS.

The talk will also show how the strict timing constraints are continuously monitored non-intrusively and how embedded analytics provides useful insights into the behavior of the base station.

On Wednesday, December 9 at 2:50 – 3:00 pm – Piotr Zierhoffer, Engineering Manager at Antmicro, will give a Tech Talk titled “Building Your World Out of Blocks with Renode and LiteX.”

Embedded systems development usually starts with gathering requirements but the more complex the device is, the more difficult it is to accurately establish the needs. Once you do that, you find or make customer hardware that meets those requirements and then the software development phase begins. However, it is likely that at some point it will turn out that not all of your original design choices were optimal so you update your hardware and software and start another development cycle, which is costly and time consuming. But it doesn’t have to be.

This talk will present modern methods of system development based on modular open source solutions, such as Antmicro’s simulation framework Renode and the soft SoC generator LiteX. Such an approach solves some of the typical problems that designers encounter when creating embedded systems, as it allows them to develop hardware in an agile and incremental way, focusing on the needs of the product rather than being limited by initial hardware choices. We will also present how Renode, which has extensive RISC-V support, enables pre-hardware development of software, giving system architects the means to evaluate their design choices at a very early stage of the cycle, and to test the whole hardware/software setup in a Continuous Integration environment, which translates into a more efficient development process and a better final product.

Featuring a number of RISC-V cores besides other architectures, the open source SoC generator, LiteX and its ecosystem are well supported in Renode, while its Zephyr and Linux ports, both actively developed by Antmicro and used in their industrial systems, as well as the dynamic community make it easy to start developing in LiteX. The presentation will explain how these modular open source solutions make for a robust set of tools that can transform advanced systems development.

To see the full schedule for the RISC-V Summit, visit the main conference website.